FPGA逻辑开发

FPGA逻辑开发

使用Baidu_HW_design_toolkit编译实现您的动态逻辑

“Baidu_HW_design_toolkit”工具包,帮助将您开发的动态逻辑实现在FPGA中。

“Baidu_HW_design_toolkit”提供FPGA硬件逻辑所需的环境,只需将自己逻辑所需的相关的文件(如rtl代码,ip核,xdc约束等)放入指定的路径,然后执行脚本,即可生成用于烧写FPGA云服务器的逻辑镜像文件。

“Baidu_HW_design_toolkit”包含了三个子文件夹,build,common_files和usr_files.

- usr_files存放用户的工程设计文件。

- common_files存放FPGA云服务镜像工程的一些通用设计。如静态逻辑的dcp,ddr约束等。通常情况下,不建议您修改common_files目录中的内容。

- build存放制作FPGA云服务器逻辑镜像所要执行的脚本,如果您具备丰富的FPGA开发经验,可以根据自己的需要修改脚本。例如,用更加适合的布局布线策略管理您的工程实现。

“Baidu_HW_design_toolkit”提供了两种流程制作FPGA云服务逻辑镜像,需要准备不同的设计文件:

- Non_IPI流程

这种方式比较类似传统的FPGA工程实现方式,您需要准备好动态部分逻辑(也就是rp_bd_wrapper.rp_bd_i)的设计文件放入usr_files指定的目录,然后执行build目录下的run_nonIPI.tcl脚本。

- IPI流程

这种方式采用vivado IP Integrator制作云服务逻辑镜像的动态部分逻辑(也就是rp_bd_wrapper.rp_bd_i)。你需要准备好IPI的设计文件放入usr_files和build下指定的目录,然后执行build目录下的run_IPI.tcl脚本。

使用bin_pr_tools更换您的动态逻辑

“bin_pr_tools”工具包,是更换FPGA动态部分逻辑的必要工具。在使用该工具包前,您需要确保FPGA的驱动程序已经加载。然后运行bin_pr_tools目录下的”load_pr_bin.sh”脚本即可更换您的动态部分逻辑。

1$sudo sh load_pr_bin.sh base ./ver2/ver2_pr_region_partial.bin

2OK set decouple! ...

3OK loading clear bin! ...

4OK loading pr region bin! ...

5OK unset decouple! ...

6OK soft reset rp_bd ...

7successfully load custom bitstream!

8partial clear bin: ./base/base_pr_region_partial_clear.bin

9partial bin: ./ver2/ver2_pr_region_partial.bin

10found clear bin base_pr_region_partial_clear.bin in the current partial bin file’s directory

11copy bin base_pr_region_partial_clear.bin into ‘last_clear_bin’ directory注意:

由于更换动态部分逻辑时,需要写入当前动态逻辑对应的clear bin,您务必保存好clear bin文件,以便下次更新动态逻辑时使用。同时bin_pr_tools工具包也会保存新动态逻辑对应的clear bin文件。

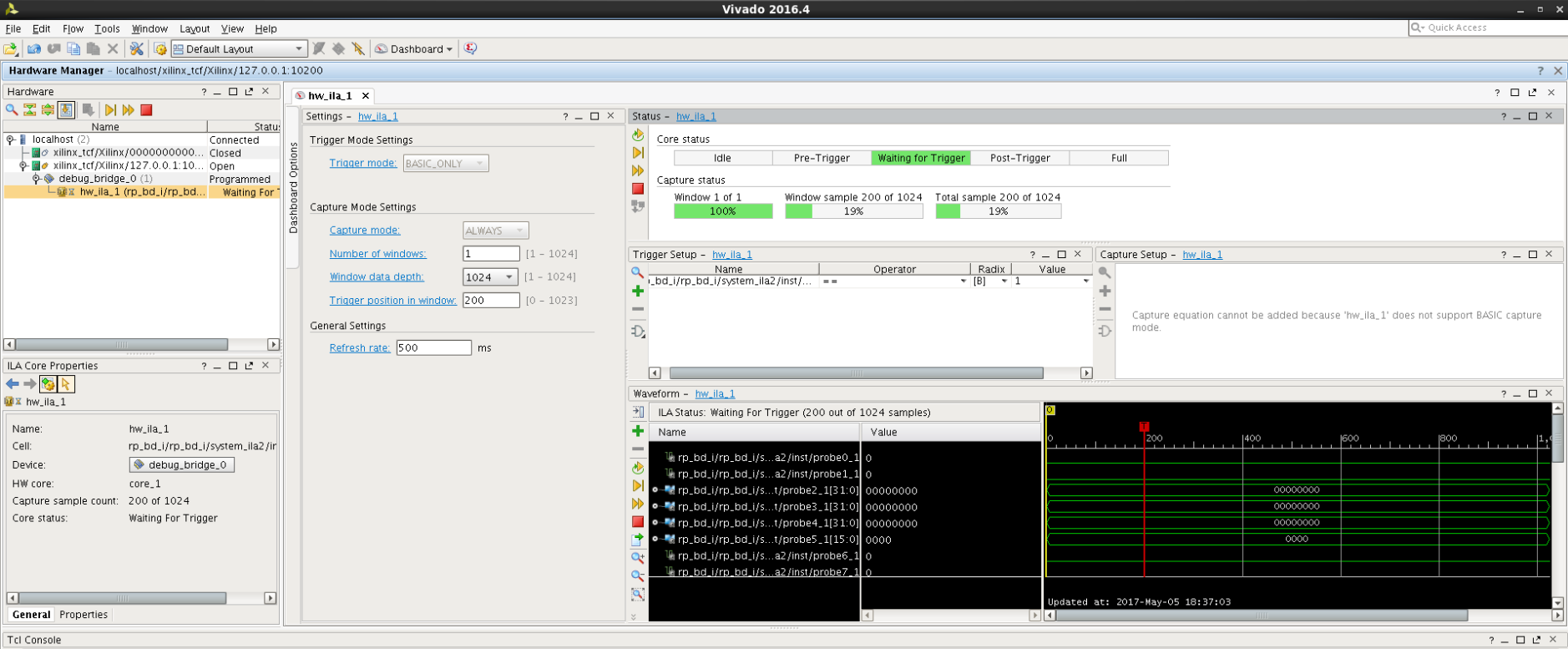

使用Vivado对您的动态逻辑进行调试

百度智能云提供工具包类似日常使用vivado操作,对您的动态逻辑进行调试。

在使用该工具包前,您需要确保FPGA的驱动程序已经加载。

- 打开xvc_server工具包,运行xvc_pcie服务。

- 使用vivado工具,仅需几步就可以通过虚拟jtag识别FPGA设备。

- 选择动态逻辑对应的probe文件,类似使用Vivado工具,对工程中的ila和vio进行功能调试和信号查看。

评价此篇文章