FPGA示例工程说明

更新时间:2019-06-20

FPGA示例工程说明

概述

为方便您掌握FPGA云服务器的使用流程,快速创建自己定制的加速卡逻辑,百度智能云提供一个demo工程作为示例。

该demo工程支持了基于FPGA云服务器开发的几个基础功能,主要包括:

- 工程分成静态和动态两部分逻辑,支持基于pcie总线的partial reconfiguration开发及配置流程。

- 静态逻辑支持pcie-3.0-8x xdma,并提供了配套的driver。用户不能修改也无需关注静态部分的逻辑。

- 动态逻辑为用户自定制部分,用户需基于当前提供的接口实现所需功能逻辑。demo工程中的动态逻辑是一个element-wise向量加法模块,基于HLS开发。接口包括:

- 一个axi slave(256bit)和一个axi lite slave(32bit)接口,可分别用于传输逻辑所需的数据和控制命令。

- 4个axi master(512bit),用于连接DDR MIG控制器(可选)。

- 中断、时钟。

- 支持基于pcie总线的ila debug,可在云服务器上的vivado中抓取信号波形进行调试。

您可根据此demo工程的结构及提供的配套脚本了解fpga云服务器的开发流程,并以该工程为基础,修改其中的动态逻辑,实现所需的其他功能。

工程结构

demo工程主要包含了两个部分,分别是static_bd_wrapper和rp_bd_wrapper。

其中static_bd_wrapper属于工程的静态部分,提供了pcie xdma,基于pcie的debug模块,flash控制器等。静态部分的逻辑不暴露给用户,用户不能修改也不用关心静态部分的逻辑。

rp_bd_wrapper则是动态逻辑,这部分逻辑中有rp_bd和其他一些组件。其中只有rp_bd是用户可以修改的内容。其他组件主要用于支持用户利用虚拟jtag进行调试或其他功能,这些组件不需要用户关心,用户不能修改。

rp_bd通过两组AXI总线与static_bd_wrapper传输数据,可以此为基础实现您所需的功能。

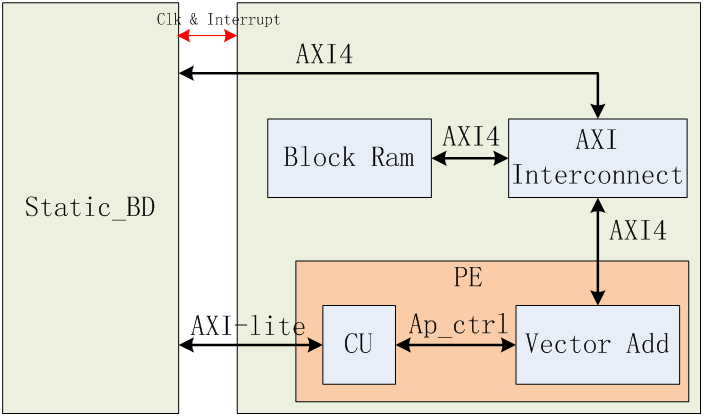

demo工程的rp_bd结构框图如下:

| 模块 | 说明 |

|---|---|

| Block Ram | rp_bd内部有一个64KB的block ram用来存储计算所用的数据和计算结果,这个block ram可同时被host和卡上的用户逻辑访问,这是通过rp_bd中的一个AXI Interconnect实现的。 |

| AXI Interconnect | AXI Interconnect用于协调两个AXI master访问rp_bd中的Block Ram;static_bd内的xdma输出的AXI4连接到AXI Interconnect的一个slave端口,demo工程提供的drive支持host通过dma访问这个block ram;PE内的Vector Add模块输出的AXI4连接到AXI Interconnect的另一个端口,使得用户逻辑也可以访问这个block ram。 |

| CU | 命令处理单元,static_bd输出的AXI-lite接口连接到PE中的CU模块,CU模块解析从AXI lite收到的命令,并产生符合ap_ctrl总线的请求信号与Vector Add模块相连。ap_ctrl是通过HLS综合出的逻辑模块采用的一种标准状态控制总线。有关其详细介绍可以参考Xilinx ug902文档。 |

| Vector Add | 计算处理单元,Vector Add模块完成向量加法运算,他是使用HLS高级综合工具开发的,它的控制输入为一组HLS模块使用的ap_ctrl信号;他使用AXI总线协议将Block Ram中的数据读出,进行加法运算后,将数据写回Block Ram中。 |

PE工作流程

- 软件发起dma_to_dev将输入向量A,B拷贝至dev;A,B的长度必须8个float数据对齐。(单精度浮点数)

- 软件通过配置寄存器发起PE计算指令,然后等待PE计算完成。

- PE计算完成后,通过中断通知CPU上的软件驱动程序。

- 软件发起dma_from_dev将输出向量C拷贝至host。(单精度浮点数)

评价此篇文章